# High Performance Multimedia Platform

### **Overview**

H700 is a high-performance quad-core 4K60 decoding multimedia platform. It integrates the 4-core 64-bit Cortex<sup>TM</sup>-A53 processor, and the new G31 GPU engine of ARM that supports OpenGL ES 3.2/Vulkan 1.1. H700 supports full-format 4K@60fps 10-bit ultra-HD video decoding, Allwinner self-developed SmartColor3.3<sup>TM</sup> picture enhancement engine, and keystone correction, which provides best user experience for video playback. It supports HDMI2.0, dual-link LVDS, RGB888 and CVBS-OUT which can meet various display output requirements. It also support BT1120 and MIPI-CSI video input which can be used for connecting camera and other display input devices. H700 also provides rich peripheral interfaces, such as USB2.0, SDIO3.0, 1000 Mbps EMAC, PWM, TSC, SCR, SPI, UART, CIR, etc. H700 can be widely applied in various multimedia products.

# **Highlights**

- Quad core ARM Cortex<sup>™</sup>-A53, 64-bit architecture

- High performance multi-core G31 GPU, supporting OpenGL ES 3.2/Vulkan 1.1

- Full formats H.265/VP9/AVS2 4K@60fps decoding, H.265 up to 6K@30fps

- Low latency H.264 4K@25fps video encoding

- SmartColor™ 3.3 picture enhancement engine

- Supports RGB888, dual link LVDS, HDMI, CVBS OUT, to achieve different display in dual screen

- Supports MIPI CSI and parallel CSI

#### **Features**

#### CPU

• Quad-core ARM Cortex™-A53

#### **GPU**

• ARM G31 MP2 GPU processor

#### Memory

- 32-bit DDR4/DDR3/DDR3L/LPDDR3/LPDDR4 interface, supporting maximum capacity of 4GB

- SD3.0/eMMC5.0 interface

- 8-bit Nand flash interface with maximum 80-bit/1KB ECC

#### **Video Engine**

#### Video decoder:

- H.265 Main10@L5.1 decoder up to 4K@60fps or 6K@30fps

- VP9 Profile 2 decoder up to 4K@60fps

- AVS2 JiZhun 10bit decoder up to 4K@60fps

- H.264 BP/MP/HP@L4.2 decoder up to 4K@30fps

- Multi-format 1080p@60fps video playback formats, including H.264 BP/MP/HP, H.263 BP, VP8, MPEG-1 MP/HL, MPEG-2 MP/HL, MPEG-4 SP/ASP@L5, AVS+/AVS JiZhun, WMV9/VC1, etc

#### Video encoder:

- H.264 BP/MP/HP encoder up to 4K@25fps or 1080p@60fps

- JPEG snapshot performance of 1080p@60fps

#### **Display and Graphic**

- Output size up to 4096 x 2048

- Six alpha blending channels for main display

- Four overlay layers in each channel, and has an independent scaler

- Potter-duff compatible blending operation

- Supports AFBC buffer

- Supports Vertical/Horizontal keystone correction

- Frame Packing/Top-and-Bottom/Side-by-Side

Full/Side-by-Side Half 3D format data

- Supports 10-bit processing path for HDR video

- Supports SDR/HDR10/HLG EOTF and color space conversion

- Supports SmartColor™ 3.3 for excellent display experience

- Supports one de-interlacing module

#### **Display Output**

- HDMI 2.0a up to 4K@60fps

- TV CVBS output, supporting PAL/NTSC

- LVDS interface with dual link, up to 1080p@60fps

- RGB interface with DE/SYNC mode, supports RGB888,

RGB666 and RGB565 with dither function, up to 1080p@60fps

#### **Display Input**

- 1 serial interface(MIPI) + 1 parallel interface

- Parallel interface supports 8-bit digital camera

- Parallel interface supports BT656, BT601, BT1120

- 4-lane MIPI CSI up to 8M@30fps

#### **Audio**

- Two DAC channels

- Supports 1 audio output interface (differential LINEOUTP/N or single-end LINEOUTL/LINEOUTR)

- One Audio HUB, supporting internal mixing function

- Embedded 3 I2S/PCM (I2S0 for extended audio codec, I2S2 for BT, I2S3 for digital power amplifier)

- Supports Left-justified, Right-justified, Standard I2S mode, PCM mode, and TDM mode

- I2S mode supports 8 channels, and 32-bit/192kbit sample rate

- One OWA OUT interface

- Integrated digital microphone(DMIC), supporting maximum 8 digital PDM microphones

#### **Security Engine**

- Supports Full Disk Encryption

- AES, DES, 3DES, and XTS encryption and decryption algorithms

- MD5, SHA, and HMAC tamper proofing

- RSA, ECC signature and verification algorithms

- Supports 160-bit hardware pseudo random number generator(PRNG)

- Supports 256-bit hardware true random number generator(TRNG)

- Integrated one EFUSE for chip ID and security application

#### Connectivity

- 3 x USB2.0 Host, 1 x USB2.0 OTG

- 2 x Ethernet MAC (one 10/100 Mbps Ethernet port with RMII interface, one 10/100/1000 Mbps Ethernet port with RGMII and RMII interfaces)

- SDIO 3.0, TSC, SCR, CIR Receiver

- 6 x TWI, 2 x SPI, 6 x UART

- 6-ch PWM, 4-ch GPADC, 1-ch LRADC

#### **Package**

- TFBGA 421balls

- 15 mm x 15 mm body size, 0.65 mm ball pitch,

0.35 mm ball size

# **Block Diagram**

| lmage In                    | Quad-core Cortex™-A53               |                   | Connectivity                 |

|-----------------------------|-------------------------------------|-------------------|------------------------------|

| Parallel CSI 16-bit bus     |                                     |                   | USB2.0 OTG                   |

| -                           |                                     |                   | USB2.0 HOST x 3              |

| 4-lane MIPI CSI             | GPU                                 | System Peripheral | UART x 6                     |

|                             | G31                                 | CCU               | SPI x 2                      |

| Display Out                 |                                     | GIC               |                              |

| DE                          | Video Engine                        | Thermal Sensor    | TWI x 6                      |

| HDMI 2.0a<br>4K@60fps       | H.265 6K@30fps<br>VP9/AVS2 4K@60fps | Timer             | TSC                          |

| RGB LCD                     | Video Decoder                       | High Speed Timer  | SCR                          |

| 1080p@60fps<br>CVBS OUT     | H.264 4K@25fps<br>Video Encoder     | PSI               | CIR Receiver                 |

| CVES COT                    |                                     | DMA               |                              |

| Audio                       | External Memory                     | IOMMU             | GPADC(4-ch)                  |

| Audio Codec                 | DDR4/DDR3/DDR3L/                    | Security System   | LRADC(1-ch)                  |

| DMIC                        | LPDDR3/LPDDR4<br>32-bit bus         | Security Boot     | PWM(6-ch)                    |

| OWA OUT                     | 8-bit Nand Flash<br>80-bit ECC      | Crypto Engine     | SDIO 3.0                     |

| SW/1951                     |                                     | SID(2Kbits)       | 12.10 0.10                   |

| Audio HUB<br>(I2S/PCM, DAM) | SD3.0/eMMC5.0<br>1/4/8-bit bus      | TrustZone         | EMAC x2(RMII,<br>RGMII/RMII) |

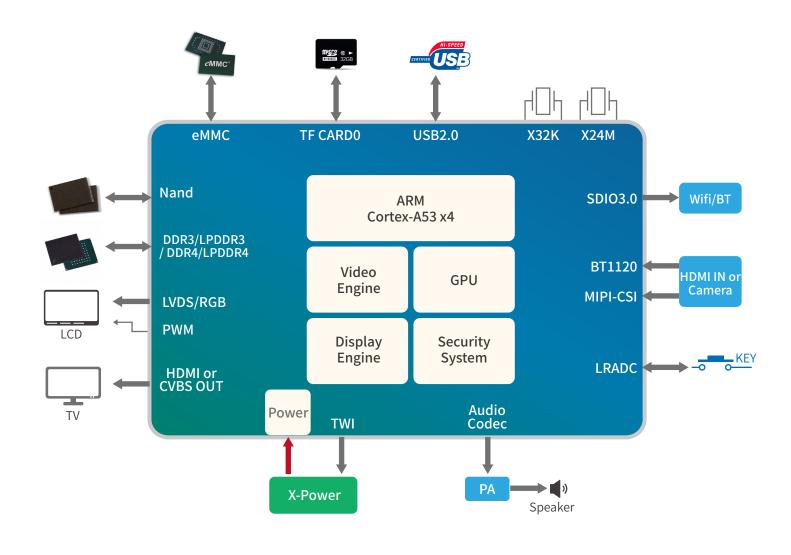

## **Typical Application Diagram**

#### **ABOUT ALLWINNER**

Allwinner Technology is a leading fabless design company dedicated to smart application processor SoCs and smart analog ICs. Its product line includes multi-core application processors for smart devices and smart power management ICs used by brands worldwide.

With its focus on cutting edge UHD video processing, high performance multi-core CPU/GPU integration, and ultra-low power consumption, Allwinner Technology is a mainstream solution provider for the global tablet, internet TV, smart home device, automotive in-dash device, smart power management, and mobile connected device markets. Allwinner Technology is headquartered in Zhuhai, China.

#### **CONTACT US**

For more product info, please contact service@allwinnertech.com, or scan the QR code to follow us on We chat.

This brief is for reference only and has no commitment. All content contained herein is subject to changes without notice. ©2020 Allwinner Technology Co., Ltd.